Highly-Efficient FFT Core in HLS

What is it?

We open-source a parameterized FFT core implementation in Vivado HLS.

Overview

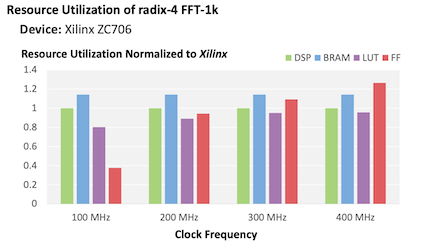

The practical use of High-level Synthesis (HLS) for FPGAs may compromise resource efficiency, which is a common design goal in FPGA programming. Specifically, when designing the iterative datapath for computing a FFT, combining naive HLS code with compiler optimizations can fail to saturate the BRAM ports and incur significant penalty in clock frequency. To solve this problem, we suggest that the target datapath should be made explicit in HLS code. Using this solution, our FFT cores reduce the FFT latency by N cycles for the radix-2 N-point FFT comparing with previous HLS-based work and the Xilinx LogiCORE FFT. Meanwhile, our designs achieve comparable peak frequency and consume similar resources to Xilinx.

Benchmarks

Compared to the Xilinx LogiCORE FFT IP, our implementations achieve slightly better latency with comparable resource utilization and peak frequency.

|

|

HLS Code Download

The HLS code for FFT is available here under non-viral license (BSD-style license). For further reading, you can also download an extended abstract regarding this topic.

References

- G. Xu, et al.

Optimizing FFT Resource Efficiency of FPGA using High-level Synthesis

IEEE High Performance Extreme Computing Conference (HPEC), 2017

Copyrights to many of the above papers are held by the publishers. The attached PDF files are preprints. It is understood that all persons copying this information will adhere to the terms and constraints invoked by each author's copyright. These works may not be reposted without the explicit permission of the copyright holder. Some links to papers above connect to IEEE Xplore with permission from IEEE, and viewers must follow all of IEEE's copyright policies.

More Information

Contact: Guanglin Xu, guanglix (at) xxxandrew.cmu.edu (delete xxx)